## 超低電圧リテンションSRAMおよび不揮発性SRAM

―エッジコンピューティングの革新的低消費電力技術―

東京工業大学 未来産業技術研究所

菅原聡

### 発表内容

- 1. 背景:スマート社会におけるコンピューティングシステム

- 2. 超低電圧リテンションSRAM技術 (ULVR-SRAM)

- 3. 不揮発性SRAM技術(NV-SRAM)

- 4. まとめと今後の展望

1. 背景:スマート社会におけるコンピューティングシステム

### スマート社会におけるコンピューティングシステム

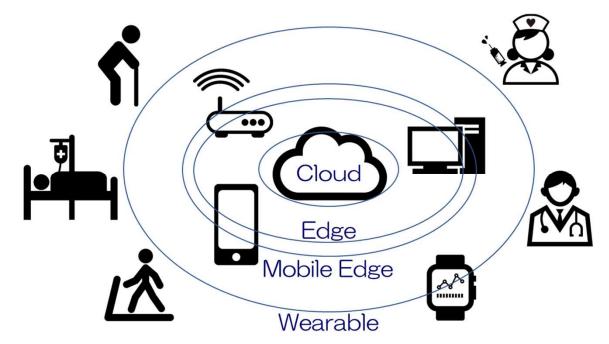

- いつでも, どこでも, 繋がる, 使えるコンピューティングシステム

- 社会実装例:Internet-of-Humans (IoH) → 医療、介護、ヘルスケア

新技術説明会

→ 深層学習(DL)などのAI技術が重要

- システムの階層構成:ウェアラブル(W) エッジ(E) クラウド(C)

- コンピューティング技術:クラウドだけでなく,W/Eでも重要

- **→** W/Eコンピューティング

- → ウェアラブルデバイス/スマートモバイルデバイス

### W/Eにおけるロジックシステムの課題

新技術説明会

- ▍対象ロジックシステム

- → マイクロプロセッサ(μP)/コントローラ(MC),システムオンチップ(SoC)

- 共通の重要課題

- → これまで以上のさらなる超低消費電力化

今回の発表 A, C

- 対策・方針(特許群)

- A. ロジックシステムの無駄な動作時/待機時電力を徹底的に削減(CMOS)

- B. エネルギー効率を限界まで高め並列化 (CMOS)

- C. 不揮発記憶の利用して待機時電力を削減 (CMOS+NVM)

- D. 高感度トランジスタの導入による超低消費電力化 (Beyond-CMOS)

- 関連技術

- E. 体温を用いたWDの電源技術(CMOS技術による熱電発電)

### 2. 超低電圧リテンションSRAM技術(ULVR-SRAM)

→ロジックシステムの無駄な動作時/待機時電力を徹底的に削減 できる新発想のメモリ技術

# エッジ向けロジックシステムの課題と対策

新技術説明会 New Technology Presentation Meetings

#### 目標

最大動作速度を維持/向上して,消費電力を大幅に削減

→無駄な電力を徹底的に削減 → 余剰な動作時電力、待機時電力の削減

#### ■余剰電力の削減方法

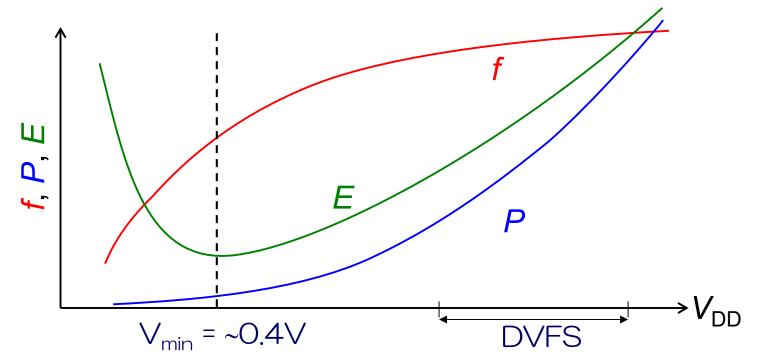

- ①消費エネルギー極小電圧(Vmin)動作による動作時電力の削減

- ②パワーゲーティング(PG)による待機時電力削減

## 動作時電力の削減とその課題:Vmin動作

#### 動作時電力の削減:

新技術説明会

- 高速動作が不要な情報処理/演算も多い(バックグラウンド処理など)

- →高速動作不要時:消費エネルギーが極小となる電圧(Vmin)で動作

- →動作時エネルギー/電力を効果的に削減(演算速度は劣化)

- 参考:DVFS(Dynamic voltage and frequency scaling)との比較

- 電源電圧の~7割程度 → 電力削減効率不十分

## 待機時電力の削減とその課題:PG

新技術説明会 New Technology Presentation Meetings

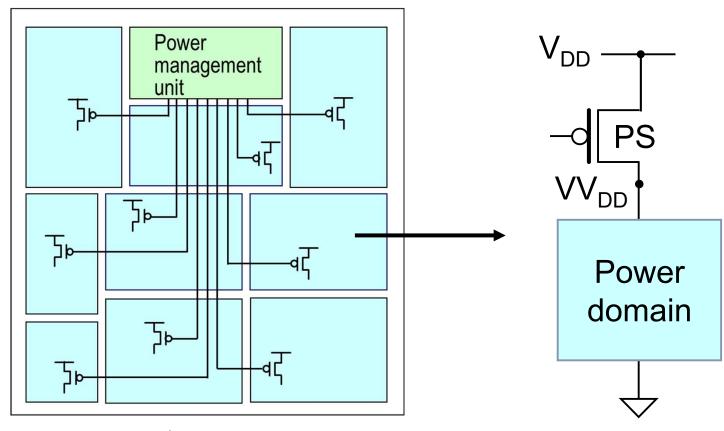

- トランジスタのリーク電流にともなう待機時電力の削減:PG

- μPやSoCをパワードメインに分割

- ドメインごとにパワーマネジメント

- →待機時ドメインの電源遮断 → 待機時電力の削減

CMOSロジックシステム

## エッジ向けロジックシステムの課題と対策

新技術説明会 New Technology Presentation Meetings

#### 目標

#### 最大動作速度を維持/向上して,消費電力を大幅に削減

→無駄な電力を徹底的に削減 → 余剰な動作時電力, 待機時電力の削減

#### ■余剰電力の削減方法

- ①消費エネルギー極小電圧(Vmin)動作による動作時電力の削減

- ②パワーゲーティング(PG)による待機時電力削減

#### 課題と対策

- 純粋なロジックドメイン: Vmin動作とPGを導入可能

- 各種メモリドメイン(SRAM): Vmin動作とPGを共に実現する技術なし

- → Vmin動作とPGを共に実現できるSRAM技術が必要

- → ULVR-SRAM

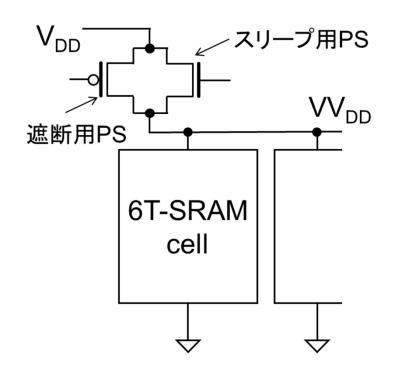

## 超低電圧リテンションを用いたPG

新技術説明会

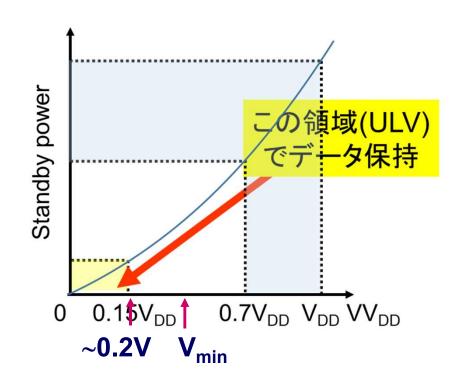

### ■ SRAMの待機時電力削減方法

- 従来SRAM→スリープモード(~O.7VDD)

- 超低電圧(ULV; ~O.2V < Vmin) リテンション(本提案)</li>

- → ULVリテンションにより90%程度以上の電力削減可能

- → 課題: ULVリテンション時のノイズマージン(NM)の確保

# 超低電圧リテンションSRAM(ULVR-SRAM)の提案

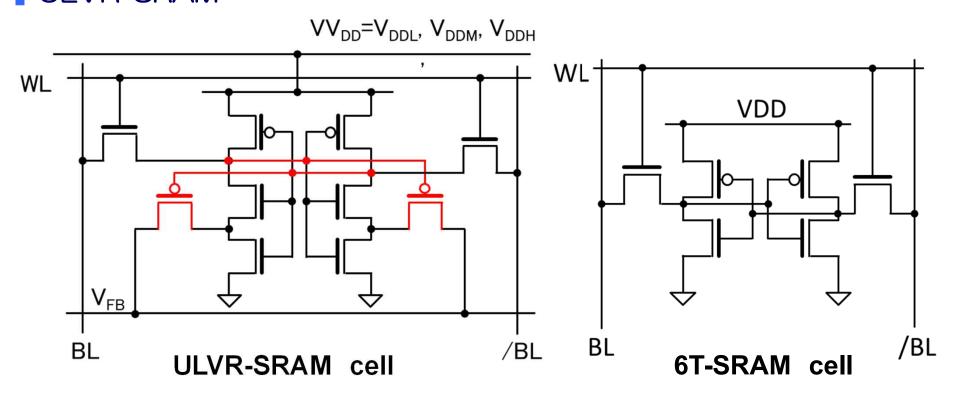

ULVR-SRAM

- VV<sub>DD</sub>の値によって動作モード変化

- 通常電圧 (~1V)→ 6T-SRAMと同等の高速動作

- Vmin (~O.4V) → 消費エネルギー極小電圧動作 (Vmin動作)

- ULV (~O.2V) → 超低電圧リテンション (PG)

STモード NM十分

# ULVR-SRAMの雑音余裕

新技術説明会

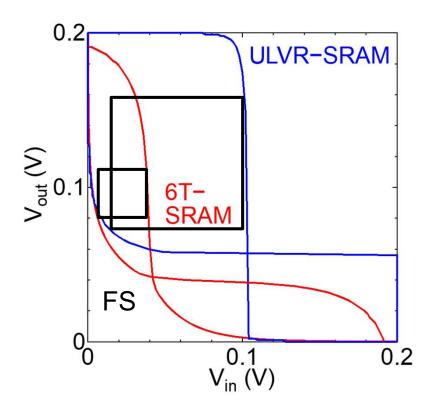

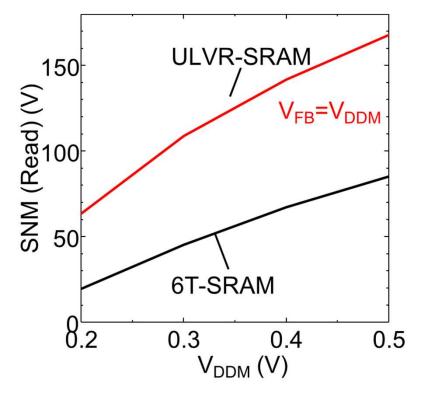

### ■ ULVR-SRAMの雑音余裕(NM)

- 従来型6T-SRAM → ULV, VminでNM劣化

- ULVR-SRAM → ULV, Vminでも十分なNM確保

超低電圧リテンション

読み出し(Vmin近傍)

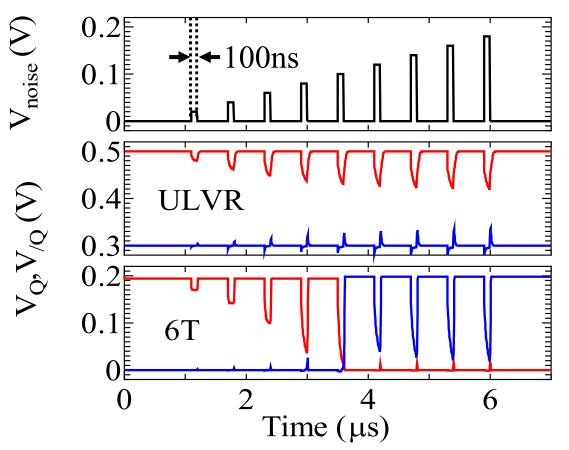

# 雑音耐性の検証

#### 新技術説明会

### ■ ULVR-SRAMの雑音耐性

- 源線(VV<sub>DD</sub>)にノイズ(記憶情報がリセットされる向き)

- 6T-SRAM → ローカルばらつきの効果によってフリップ

- ULVR-SRAM

- → フリップなし

- → ノイズ耐性:極めて高

- → ULVRによるPG Vmin動作

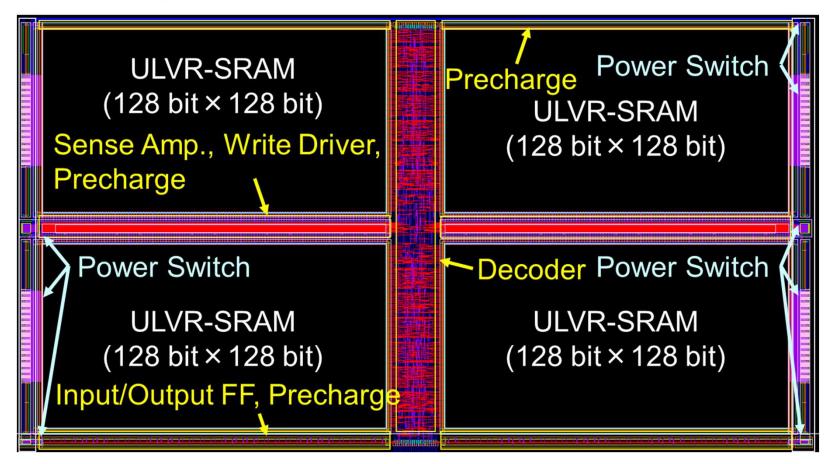

### ULVR-SRAMマクロ

新技術説明会

#### 8kBマクロの開発と評価

- VDD=1.2V, CLK=600MHz

- ULV(O.2V)によるPG:待機時電力の削減率95%(6T-SRAM比較)

- Vmin動作(0.4V, 50MHz):動作時電力削減率98%

### 3. 不揮発性SRAM技術(NV-SRAM)

→不揮発記憶の利用して待機時電力を削減

## 不揮発性メモリ(NVM)の応用

新技術説明会

- 抵抗変化型NVM (MRAM, ReRAM, PRAM)

- 記憶内容を保持したまま電源遮断可能 → 待機時電力の削減可能

- 簡単なセル構造 → 高密度集積化可能

#### 課題

- 書き込み速度が遅い、書き込みエネルギーが大きい

- 読み出し速度はSRAMほど早くない

### 【マイクロプロセッサ応用

- 待機時電力の削減, 高密度集積化は有望

- NVM素子へのストアによるエネルギーオーバーヘッドが大きい

### ■ 不揮発性SRAM (NV-SRAM)

- NVM素子+CMOSで構成した電源遮断しも情報が消えないSRAM

- 通常のSRAM動作と不揮発記憶の分離 → プロセッサ応用可能

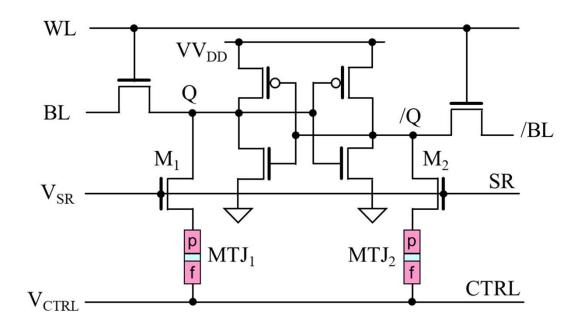

## 強磁性トンネル接合(MTJ)を用いたNV-SRAM

#### 新技術説明会

### セル構成

- 6TセルとMTJを電気的に分離 → 高効率PG応用

- 通常SRAM動作 → MTJを電気的に分離, 6Tセルと同等の高性能動作

- 電源遮断 → MTJに書き込み, 待機時電力を99.9%以上削減可能

- 電源復帰 → MTJから双安定回路に自動的にデータ復帰

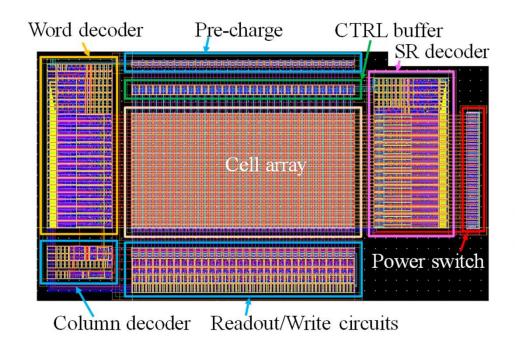

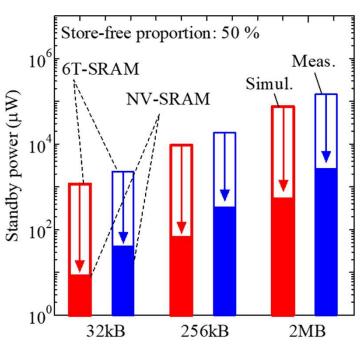

### NV-SRAMのアーキテクチャと性能評価

新技術説明会

- 2kbTEGを用いた性能評価

- 待機時電力の削減率:99.9%以上

- Break-even time (BET)  $\rightarrow$  ~100 $\mu$ s(32kB)-~1ms(2MB)

- MTJへのストアエネルギーの削減アーキテクチャ(BET削減)

- 階層型ストアフリー(HSF): 既書き込みのMTJへのストアを回避

- 不要データの積極的フラッシュ(PUDF)

## 4. まとめと今後の展望

### まとめ

#### 新技術説明会

- 対象ロジックシステム:マイクロプロセッサ/マイクロコントローラ, SoC

- ▶ 共通の重要課題:これまで以上のさらなる超低消費電力化

- 対策・方針

- ロジックシステムの無駄な動作時/待機時電力を徹底的に削減 (CMOS)

- → ULVR-SRAM技術

- 不揮発記憶の利用して待機時電力を削減(CMOS+NVM)

- → NV-SRAM技術

- 発展・派生技術

- 超低消費電力化 → クラウド/データセンターにも応用可能

- → Cryo-CMOS (ハイブリッド量子コンピュータ技術)

- → 宇宙用マイクロプロセッサ

### 本技術に関する知的財産

1) 【発明の名称】: スピン注入磁化反転MTJを用いた不揮発性SRAM/ラッチ回路

【出願番号】 : PCT/JP2013/063393 (日・米・中 登録済)

【特許権者】 : 国立研究開発法人科学技術振興機構

【発明者】 : 山本 修一郎、菅原 聡

2) 【発明の名称】:記憶回路

【出願番号】 : PCT/JP2017/006811 (日・米・欧・韓・中・台 登録済)

【特許権者】 : 国立研究開発法人科学技術振興機構

【発明者】 : 山本 修一郎、周藤 悠介、菅原 聡

3) 【発明の名称】: 電子回路

【出願番号】 : PCT/JP2016/059453 (日・米・欧・韓・中・台 登録済)

【特許権者】 : 国立研究開発法人科学技術振興機構

【発明者】 : 菅原 聡、山本 修一郎

3) 【発明の名称】: 電子回路および双安定回路

【出願番号】 : PCT/JP2020/012099, TW 109110825

【特許権者】:国立研究開発法人科学技術振興機構

【発明者】 : 菅原 聡、山本 修一郎

### お問合せ先

新技術説明会

国立研究開発法人科学技術振興機構

知的財産マネジメント推進部 知財集約・活用グループ

TEL:03-5214-8486

e-mail: license@jst.go.jp