# 新材料による 革新的強誘電体メモリの創製

東京工業大学 工学院 電気電子系 准教授 大見 俊一郎

2021年11月2日

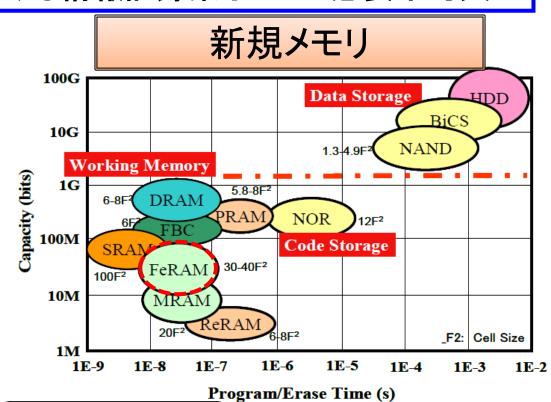

### 不揮発性メモリの比較と強誘電体メモリ

#### 不揮発性メモリ

あらゆる電子システムにおける情報記録素子として必要不可欠

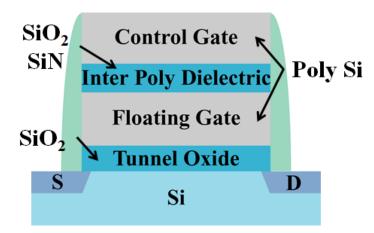

#### フラッシュメモリ

- ◆動作電圧高: ~20 V

- ◆ 動作速度低

- ◆書き換え寿命短

Floating Gate: 70 - 100 nm

微細化困難 3次元集積化積層限界

#### FeRAM 強誘電体メモリ

- ◆ 低電圧動作

- ◆高速動作

- ◆ 高書き換え回数

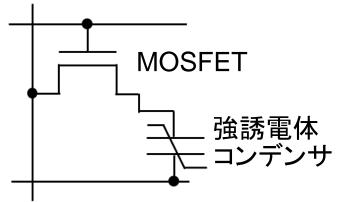

### 強誘電体メモリの構成

#### 強誘電体

- ◆ 自発分極(残留分極)

- ◆ 抗電界以上の電界印加で分極反転

1transistor/1capacitor型 (1T1C/2T2C)

- ◆ 破壊読出し

- ◆ 集積度低

- Suica、RF-IDタグ

- -16-64 Mbit

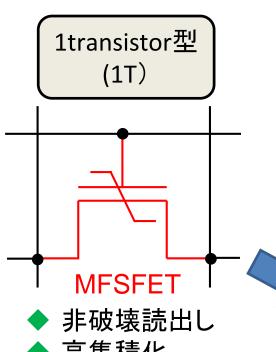

◆ 高集積化

- 1958年に提案

- ・実用化されていない

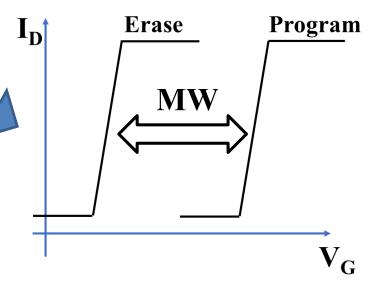

分極*P* "0" 電界*E* "1"

強誘電体薄膜のSi基板上へ直接形成

MFSFET: Metal/Ferroelectrics/Si Field-Effect Transistor

### 従来の強誘電体材料

| 強誘電体  | PZT [Pb(Zr,Ti)O <sub>3</sub> ]<br>(チタン酸ジルコン酸鉛)         | SBT [SrBi <sub>2</sub> Ta <sub>2</sub> O <sub>9</sub> ]<br>(タンタル酸ビスマス酸 ストロンチウム) | BFO [BiFeO <sub>3</sub> ]<br>(ビスマスフェライト) |

|-------|--------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------|

| 結晶構造  | Pb :Zr/Ti :O                                           | :Sr :Bi :Ta :O                                                                  | :Bi :Fe :0                               |

| メリット  | ・低温プロセスが可能<br>・量産性が高い<br>(富士通で量産中)                     | ・反転電圧が1.8[V]以下<br>・電圧が低い為、疲労特性<br>が向上する。                                        | ・Qswが180~220[uC/cm2]<br>とPZTの約5倍。        |

| デメリット | <ul><li>・反転電圧がやや高い。</li><li>(メリット: データが化け難い)</li></ul> | ・Qswが小さい<br>・プロセスが高温                                                            | ・新素材であり研究開発中<br>(☆東京工業大学との共同研究☆          |

NEDO「強誘電体メモリの研究開発」(東京工業大学 他10社) (研究代表者 石原宏教授、1999-2003)により実用化に貢献

課題:薄膜化困難、Si基板上への形成困難(Bi, Pb等の拡散)

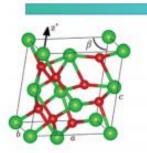

## 強誘電性酸化ハフニウム(Fe-HfO<sub>2</sub>)

新技術説明会 New Technology Presentation Meetings!

Si上強誘電性Si添加HfO<sub>2</sub>

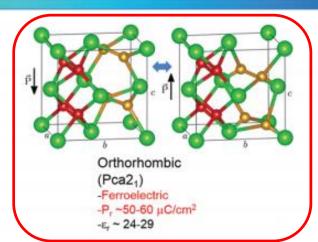

斜方晶(準安定相)

•10 nm級極薄膜化

Monoclinic (P2<sub>1</sub>/c) -Dielectric - ε<sub>r</sub> ~ 19-25

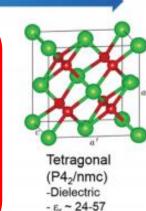

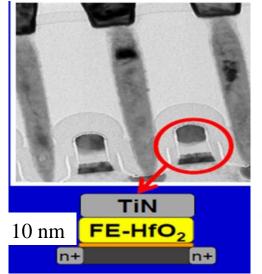

#### 微細化(28 nm)

#### 強誘電性HfO2

- •MFSFETの実現

- •微細化、高集積化

不揮発性メモリの高速化・ 低消費電力化を実現

## Fe-HfO<sub>2</sub>薄膜のインパクト

Table MM04 - More Moore Memory - NVM Technology Roadmap

| Table white - more moore memory - NVM Teenhology Roadmap |                           |                   |                   |                |           |             |             |  |  |

|----------------------------------------------------------|---------------------------|-------------------|-------------------|----------------|-----------|-------------|-------------|--|--|

| YEAR OF PRODUCTION                                       | 2018                      | 2020              | 2022              | 2025           | 2028      | 2031        | 2034        |  |  |

|                                                          | G54M36                    | G48M30            | G45M24            | G42M21         | G40M16    | G40M16T2    | G40M16T4    |  |  |

| Logic industry "Node Range" Lab - ' '                    | 11711                     | nen               | 11011             | 110 411        | "1.5"     | "1.0 eq"    | "0.7 eq"    |  |  |

| IDM-Foundry node labeling 100G                           |                           |                   |                   |                | i2.1-f1.5 | i1.5e-f1.0e | i1.0e-f0.7e |  |  |

| Mainstream device for logic                              | MEGEET                    | Data              | Storage           | HDD )          | LGAA      | LGAA-3D     | LGAA-3D     |  |  |

| NVM TECHNOLOGY                                           | (MFSFET)                  |                   | Bi                | CS             |           |             |             |  |  |

| A. FeRAM (Ferroelectric RAM) [1]                         |                           |                   |                   |                |           |             |             |  |  |

| FeRAM technology node – F (nm) [2                        | king                      | 1.3-4             | .9F2 NANI         | <mark>'</mark> | 45        | 45          | 45          |  |  |

| MET1 1/2 Pitch - F(nm)                                   |                           |                   |                   | • - • •        | 80        | 80          | 80          |  |  |

| For DAM collision and forton a in m                      | 6-8F <sup>2</sup> D M 5.8 | 3-8F <sup>2</sup> |                   |                | 19        | 19          | 19          |  |  |

| FeRAM cell size ( um2)                                   | 6F PRA                    | AM NOR            | ) <sub>12F²</sub> |                | 0.12      | 0.12        | 0.12        |  |  |

| FeRAM cell structure [4]                                 |                           |                   |                   |                | 1T1C      | 1T1C        | 1T1C        |  |  |

| FeRAM capacitor structure [5]                            | SRAM                      | Code Sto          | orage             |                | stack     | stack       | stack       |  |  |

| FeRAM capacitor footprint (µm2) [6]                      | FeRAM 30-4                | 10F <sup>2</sup>  |                   |                | 0.067     | 0.067       | 0.067       |  |  |

| FeRAM capacitor active area (µm2) 10M                    | MRAM                      |                   |                   |                | 0.067     | 0.067       | 0.067       |  |  |

| FeRAM cap active area/footprint rati                     |                           | M                 |                   |                | 1         | 1           | 1           |  |  |

| Ferro capacitor voltage (V) [9]                          | 20F2 ReRA                 | 6-8F <sup>2</sup> |                   | F2: Cell Size  | 1         | 1           | 1           |  |  |

| FeRAM minimum switching charge ( 1M -                    | 17.0 17.                  | 47 4 47           |                   |                | 26.5      | 26.5        | 26.5        |  |  |

| FeRAM endurance (read/write cycle 1E-9                   | 1E-8 1E-7                 | 1E-6 1E-          | 5 1E-4            | 1E-3 1E-2      | >1.0E16   | >1.0E16     | >1.0E16     |  |  |

| FeRAM nonvolatile data retention (y                      | Prog                      | ram/Erase Ti      | me (s)            |                | 10 Years  | 10 Years    | 10 Years    |  |  |

|                                                          |                           | •                 |                   |                |           |             |             |  |  |

- -ロードマップのセル構造は1T/1C

- -2022年以降セル構造の変更が必要

- •MFSFETにより微細化・高集積化を実現

### Fe-HfO<sub>2</sub>の課題

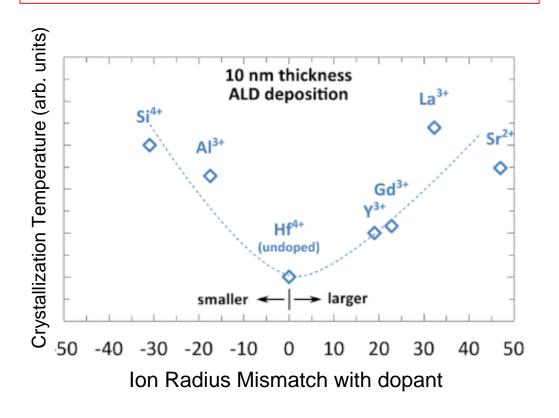

Zr、Siなどを添加し準安定相に結晶 化させるため、高温熱処理が必要

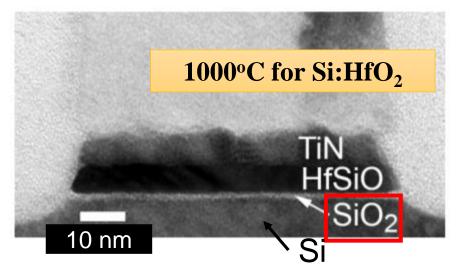

低誘電率界面層の 形成

#### 低誘電率界面層

- → 減分極電界によるメモリ特性の劣化 添加元素

- → しきい値電圧のばらつき

#### ノンドープFe-HfO2

- 低温プロセス

- しきい値電圧ばらつき低減

[1] T. Schenk, Formation of Ferroelectricity in Hafnium Oxide Based Thin Films, Books on Demand (2017). [2] T. S. Böscke et al., IEDM11-550 (2011).

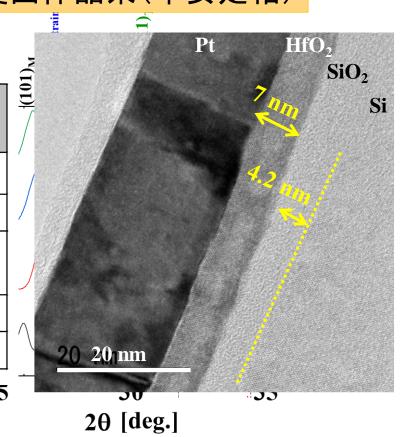

## ノンドープFe-HfO<sub>2</sub>

#### 反応性スパッタ法における酸素流量比の制御によりSi基板上への形成を実現

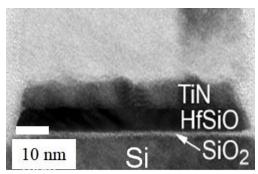

#### ノンドープFe-HfO<sub>2</sub>(5 nm, 500°C)

#### 菱面体晶系(準安定相)

| Ferroelectric<br>Undoped-HfO <sub>2</sub> FET | TiN/HfO <sub>2</sub> /SiO <sub>2</sub><br>(This work) | Pt/HfO <sub>2</sub> /SiO <sub>2</sub><br>[17] | TaN/HfO <sub>2</sub> /SiO <sub>2</sub> [18] |  |

|-----------------------------------------------|-------------------------------------------------------|-----------------------------------------------|---------------------------------------------|--|

| FE-Oxide                                      | HfO <sub>2</sub> (ALD)                                | HfO <sub>2</sub> (sputter)                    | HfO <sub>2</sub> (ALD)                      |  |

| Thickness                                     | 6 nm                                                  | 10 nm                                         | 4 nm                                        |  |

| Memory Window<br>(?V <sub>t</sub> )           | 0.5 ∨<br>(V <sub>P/E</sub> =±5 ∨)                     | 1.2 V<br>(DC sweep, ±2.5 V)                   | 0.045 V<br>(DC sweep)                       |  |

| Retention (sec)                               | > 104                                                 | NA                                            | NA                                          |  |

| Endurance (cycles)                            | 5x 10 <sup>4</sup>                                    | NA                                            | NA                                          |  |

Gate Voltage [V]

菱面体晶系の結晶がSi基板上で歪を生じることにより強誘電性が発現

<sup>[1]</sup> J.W. Shin, S. Ohmi et al, DRC, 29 (2021).

<sup>[2]</sup> S. Ohmi et al, IEEE TED, **68**, 2427 (2021).

<sup>[3]</sup> J.-D. Luo et al, IEEE EDL, 42, 1151 (2021)

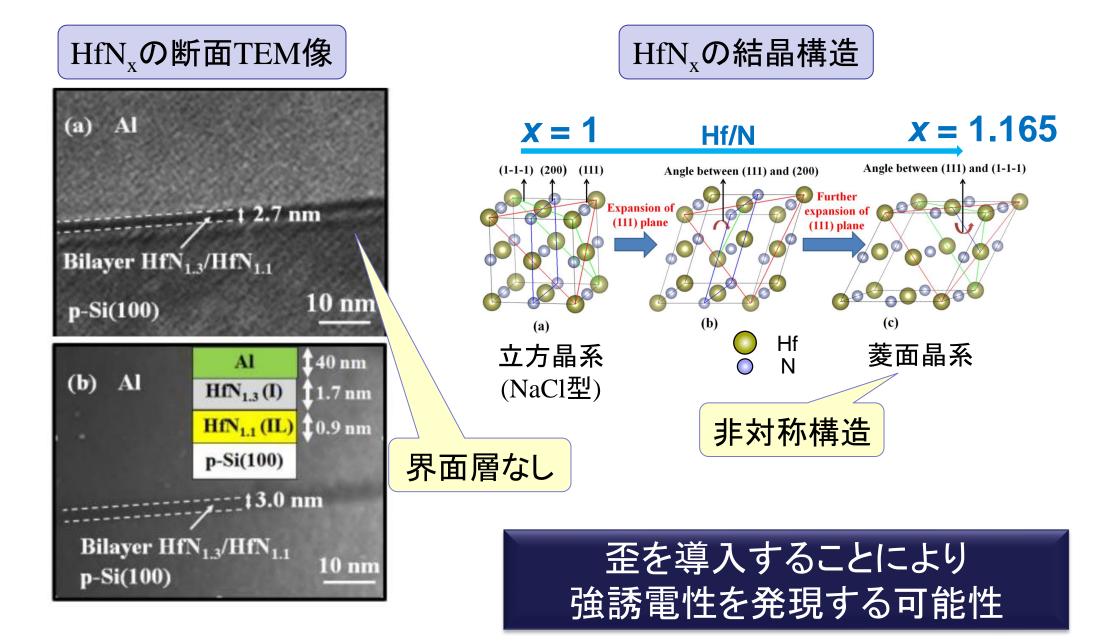

## 窒化ハフニウム(HfN<sub>x</sub>)に関する先行研究

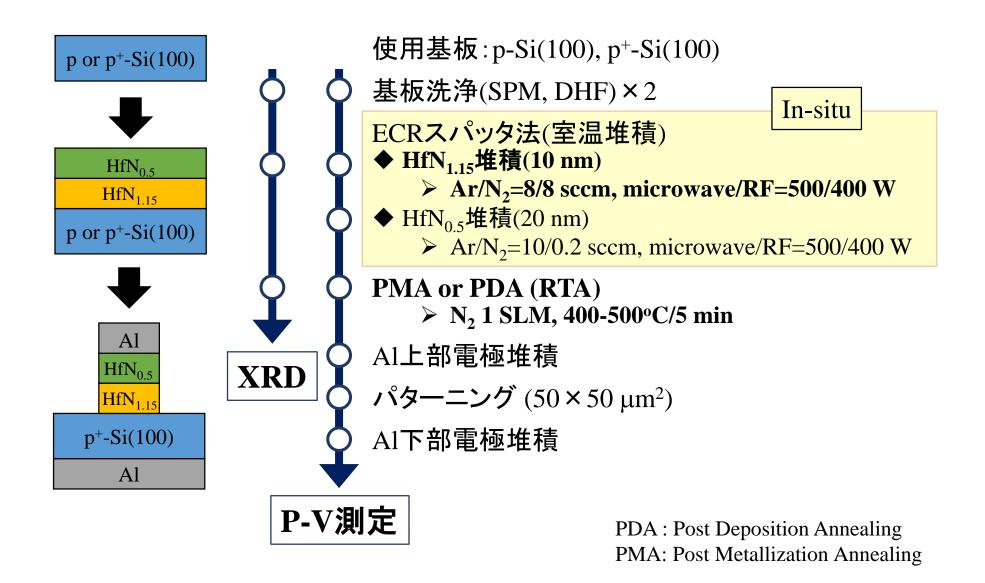

## HfNxを用いたMFSダイオードの作製プロセス

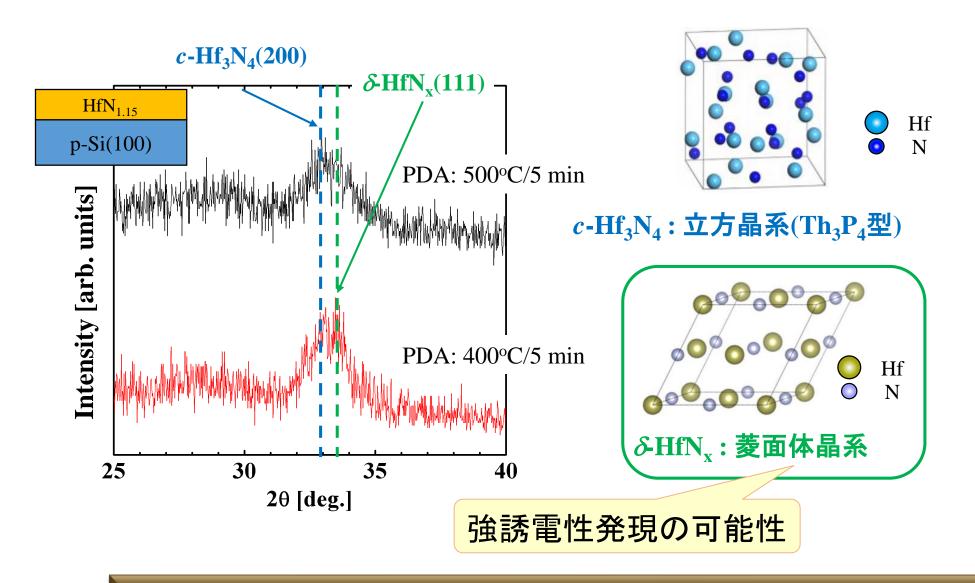

### Si(100)基板上に形成したHfN<sub>x</sub>薄膜の結晶性

HfN<sub>1.15</sub>は、400°C/5 minでアニールすると菱面体晶系で結晶化

[1] C. Hu et. al, Scripta Materialia 108, pp.141-146 (2015). [2] Z. Gu et. al, Acta Materialia 90.

[3] S. Ohmi et al, IEEE JEDS (2021). [under review]

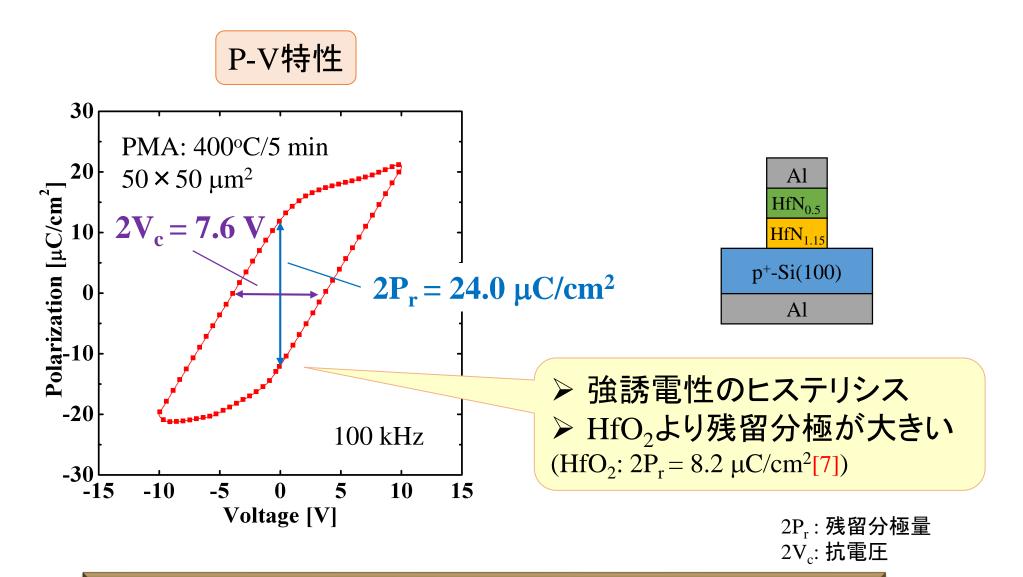

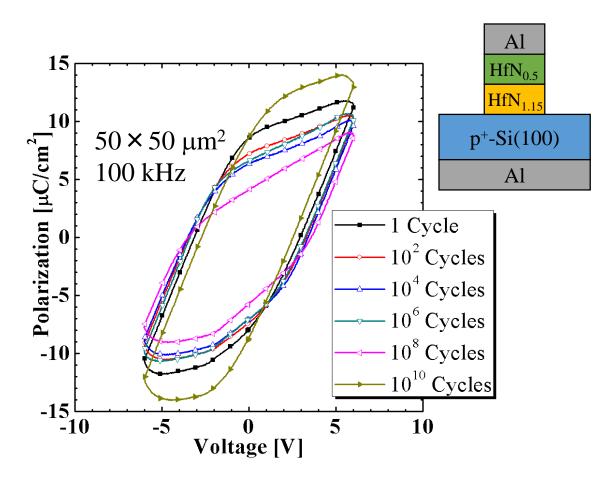

### HfN<sub>x</sub>薄膜の分極-電圧特性

400°C/5 minでアニールしたHfN<sub>1.15</sub>薄膜が強誘電性を発現

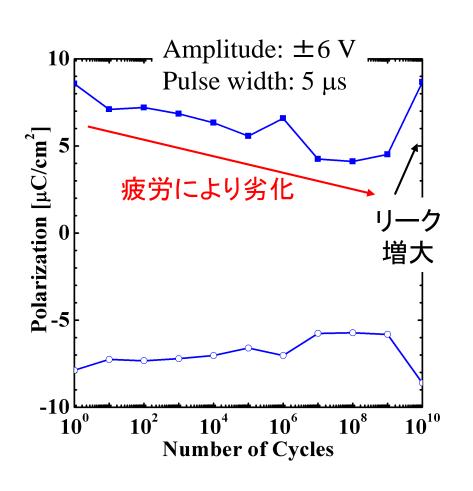

### HfN<sub>x</sub>薄膜の分極-電圧特性

- ▶ 10<sup>9</sup>回のスイッチングへの耐性

- ▶ インプリント現象なし

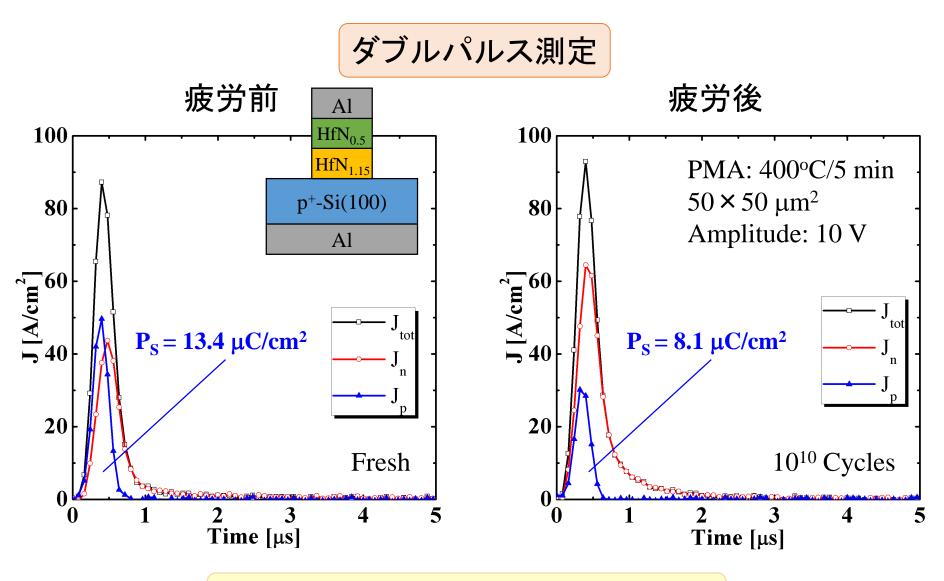

### 疲労特性評価前後のスイッチング電流

▶ 109回パルス印加後に分極量低下

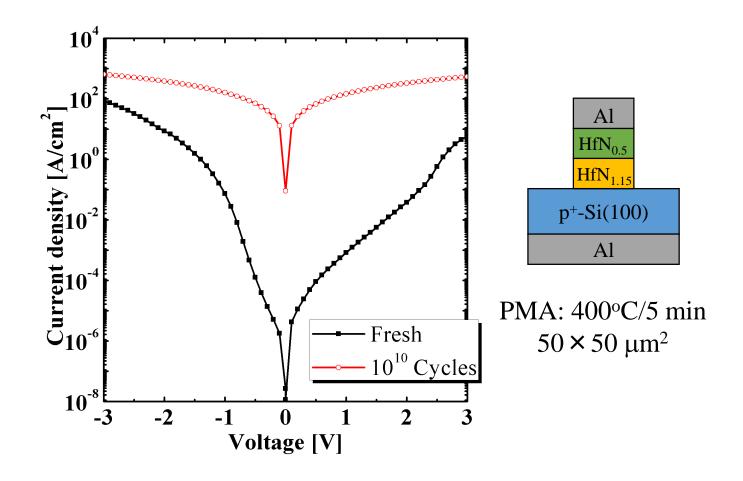

### 疲労特性評価前後のリーク電流

➤ 10<sup>9</sup>回パルス印加後にリーク電流増大

### 強誘電性HfN<sub>x</sub>(Fe-HfN<sub>x</sub>)薄膜の特徴

- Fe-HfO<sub>2</sub>の問題点であった、低誘電率界面層の形成を抑制でき、Si基板上への強誘電体薄膜の直接形成に成功した。

- 低誘電率界面層の形成を抑制できたため、保持特性などを向上することが可能となった。

## 想定される用途

- ・保持特性、疲労特性を向上した1T型強誘電体メモリに適用することで高集積化、低消費電力化のメリットが大きいと考えられる。

- 達成された強誘電性に着目すると、人工知能 回路用のアナログメモリへの応用に展開する ことも可能と思われる。

## 実用化に向けた課題

- 現在、膜厚10 nmでの強誘電性まで開発済み。 しかし、10 nm以下への薄膜化が未解決である。また、抗電界が3.8 MV/cmと大きい点が 課題である。

- 今後、薄膜化と結晶性の向上について実験 データを取得し、強誘電体メモリを低電圧動 作化していく場合の条件設定を行っていく。

- 実用化に向けて、しきい値電圧制御の精度を 20 mVまで向上できるよう技術を確立する必 要もあり。

## 企業への期待

- 未解決の薄膜化と結晶性の向上については、 スパッタ形成プロセスと熱処理プロセスにより 克服できると考えている。

- デバイスの集積化、薄膜形成および評価技術 を持つ、企業との共同研究を希望。

- ・また、不揮発性メモリを開発中の企業、新規 薄膜材料分野への展開を考えている企業に は、本技術の導入が有効と思われる。

## 本技術に関する知的財産権

・発明の名称:強誘電性薄膜の形成方法、

それを備える半導体装置

• 出願番号 : 特願2021-039611

• 出願人 : 東京工業大学

• 発明者 : 大見俊一郎

## 産学連携の経歴

- 2015年-2017年 素材関連のA社と共同研究実施

- 2021年-2022年 装置関連のB社と共同研究実施

## お問い合わせ先

東京工業大学 研究・産学連携本部

TEL 03-5734-2445

FAX 03-5734-2482

e-mail sangaku@sangaku.titech.ac.jp